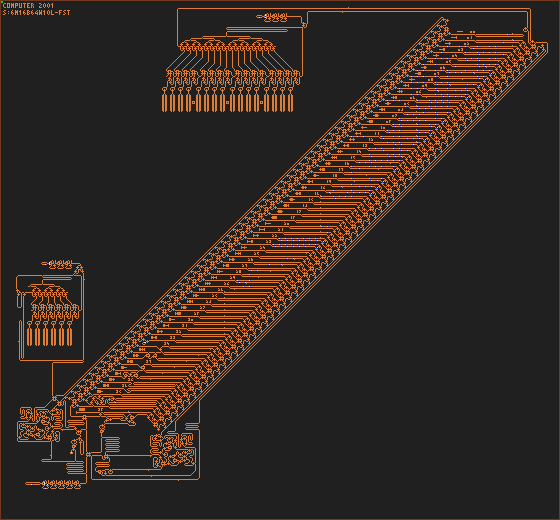

Original computer, by David Moore and Mark Owen, with the help of many others

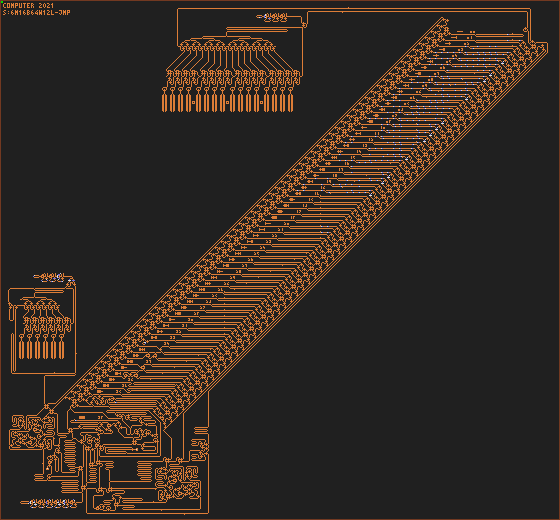

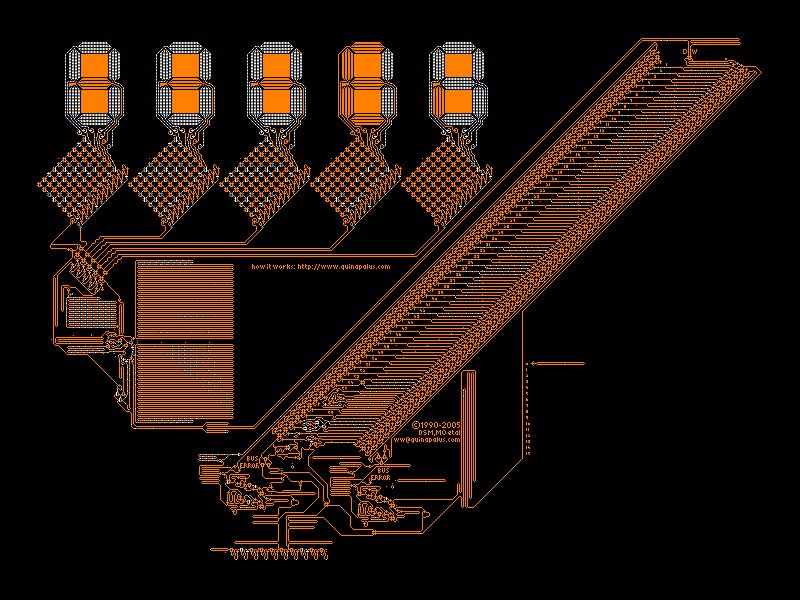

Landscape computer

The original computer dates from 1992 and is the work of David Moore and Mark Owen, with the help of many others.

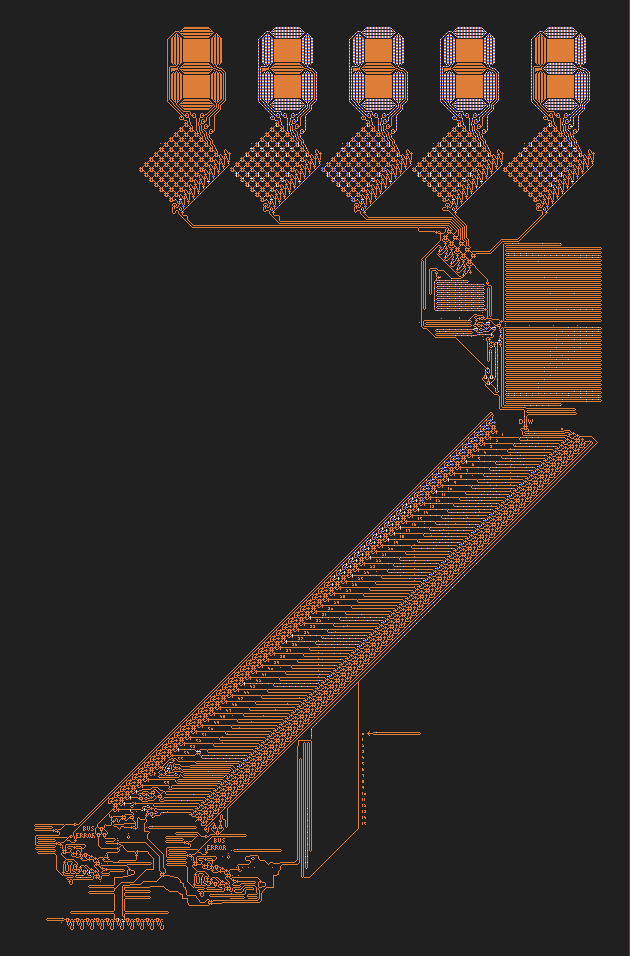

The computer is (from top to bottom) build up from: a seven-segment 5-digit display module, a binary-to-BCD converter, a registerbank with 64 registers, a control unit containing a read pulse generator and a write pulse generator, and a master clock unit.

The original computer takes 1152 generations for a single cycle. This is composed of 768 generations to go through the register bank (6 x 64 x 2) and 384 generations for the control and address processing unit. This is the same as 12 loops of 96 generations each.

The landscape version of the original computer is specially created to accomodate the favorite 800x600 computer screen size, and can be used as Windows background. This computer has exactly the same functionality as the original computer.